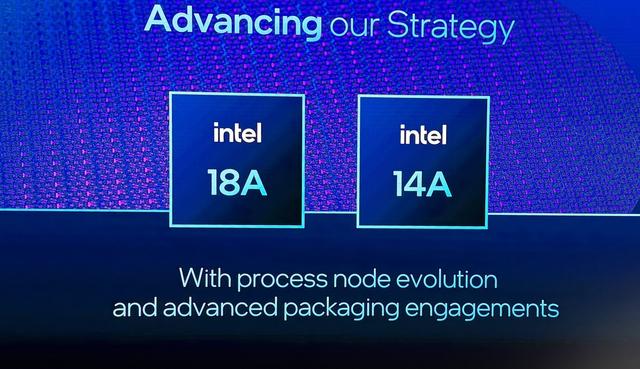

在刚刚举办的2025英特尔代工大会上,英特尔公布了包含18A-P、14A等在内的最新制程技术路线图,并展示了其在先进封装领域的技术创新与突破,同时分享了自身与生态系统伙伴间广泛且深度合作。

刚刚上任六周的英特尔公司首席执行官陈立武(Lip-BuTan)先生在主题演讲中分享了英特尔代工的最新进展和未来发展重点,同时强调了英特尔正在着手推动其代工战略的下一阶段演进。此外,英特尔代工首席技术与运营官Naga Chandrasekaran以及代工服务总经理Kevin O’Buckley也分别发表了主题演讲,展示了制程和先进封装的最新进展,并重点介绍了英特尔代工遍布全球的多元化制造和供应链布局,以及生态系统的支持。

“Trust”,是本次英特尔代工大会主题演讲环节中出现的最为频繁的词汇:工具和IP生态系统合作伙伴,客户服务和可预测执行以及技术+全球能力,构成了英特尔以客户为中心的值得信赖的技术和制造理念。而值得信赖且历经验证的生态系统合作伙伴,也为英特尔代工提供了全面的IP、EDA和设计服务解决方案组合,支持英特尔代工的发展,推动技术进步。

作为标志性的全栈式系统级代工,英特尔代工一直以来致力于向客户交付领先的制程工艺和先进封装技术。英特尔代工拥有业界领先的技术、丰富的IP组合、一流的芯片设计生态系统和灵活运营的全球化制造供应链,并且可以将这些优势结合起来,为客户提供优质代工服务。

·丰富的先进封装技术组合为客户提供多元化服务

英特尔公司首席执行官陈立武表示:“英特尔致力于打造世界一流的代工厂,以满足日益增长的对前沿制程技术、先进封装和制造的需求。我们的首要任务是倾听客户的声音,提供有助于其成功的解决方案,以赢得客户的信任。我们在英特尔全公司范围内推动以工程至上为核心的文化,同时加强与整个代工生态系统的合作关系,这将有助于我们推进战略,提高执行力,在市场上取得长期成功。”

当前以及未来很长一段时间里,半导体依然是现代社会和未来社会的基石,尤其是在AI驱动的时代里,半导体的重要性将会进一步加深。陈立武认为,半导体产业将在2030年突破万亿美元规模,而AI将成为极其重要的推动力。同时,英特尔将在这一过程中扮演关键角色。

英特尔代工服务一直致力于构建无缝的先进封装流程,以打造更出色的通用设计。对于即将到来的Intel 18A先进制程节点而言,任何客户都能够通过丰富的EDA方案进行设计,并且借助英特尔代工旗下多元化的先进封装技术快速完成从设计到制造再到封装的全流程制造环节。

针对先进封装需求,英特尔代工提供系统级集成服务,使用Intel 14A和Intel 18A-P等制程节点,通过Foveros Direct(3D堆叠)和EMIB(2.5D桥接)技术实现连接。同时英特尔还将为客户提供新的先进封装技术,包括面向未来高带宽内存需求的EMIB-T;在Foveros3D先进封装技术方面,Foveros-R和Foveros-B也将为客户提供更多高效灵活的选择。

事实上,拥有强大的制程工艺技术固然重要,但先进封装能力同样不可或缺,因为利用封装优势对于提升芯片性能至关重要。同时,先进封装技术可以进一步补充并提升Intel 18A和Intel 18A-P等先进制程的价值。

在过去50年里,英特尔封装技术不断发展,并始终处于行业领先地位。无论是引线键合架构(Wire-BondQFN/QFP)、倒装陶瓷芯片(Flip-ChipCeramic)、倒装有机多芯片(Flip-ChipOrganicMulti-Chip)等经典的传统封装形式。还是时下EMIB、Foveros这样的2.5D、3D封装技术的探索与实践,英特尔在封装层面的技术积累相当深厚。

也正是得益于这样的技术积累,英特尔代工有着非常完整的先进封装产品组合。包括两种不同版本的FCBGA(Flip-ChipBall Grid Array),即FCBGA 2D和FCBGA 2D+。在传统的有机FCBGA封装基础上,对于那些不需要高速I/O、或不需要芯片间极高带宽的产品来说,可以实现低成本量产。

EMIB(嵌入式多芯片互连桥接)则是英特尔相当知名的封装技术,从2017年开始投入使用之后,不少英特尔芯片都是基于EMIB技术来进行封装的。时下,它不仅包含EMIB 2.5D,同时还衍生出了EMIB 3.5D。前者支持单层芯片以及HBM(高带宽存储)堆叠,芯片间通过基板上的微型硅桥实现连接。当客户需要要高密度的芯片间连接,同时希望在芯片间实现低功耗连接时,EMIB是非常理想的封装方式。

而EMIB 3.5D与EMIB 2.5D类似,都采用嵌入基板中的硅桥技术。但不同之处在于,EMIB 3.5D引入了3D堆叠技术。就像我们在地基上建楼房那样,一层一层将芯片堆叠起来。而且芯片可以被堆叠在有源或者如中介层那样的无源基板上。因此,EMIB 3.5D不仅具备EMIB的优势,还增加了堆叠的灵活性。对于适合垂直堆叠的IP来说更加合适。

再者就是自2019年开始引入的Foveros技术,包括Foveros 2.5D和Foveros 3D。与EMIB 3.5D类似,Foveros技术可以与其它中介层技术结合起来使用。Foveros 2.5D可以在芯片与晶圆的连接上采用基于焊料的连接方式,而非基底连接。当芯片组将高速I/O与较小的芯片组分离时,就会采用这种方法。

而现在,英特尔在Foveros技术家族中引入了Foveros Direct技术。它不是焊料与焊料的连接,而是采用铜与铜直接键合。这种连接方式能够实现最高的带宽和最低的功耗互连,从而让芯片具备卓越的性能与能效。此外在AI和HPC相关产品中,实际上可以结合使用多种技术来进行封装。例如采用Foveros Direct 3D的同时与HBM连接,最终形成EMIB 3.5D封装。这些不同的封装技术之间并非互斥关系,而是可以被灵活地运行到到一个完整的封装中。

过去几年,行业内的2.5D封装产能面临诸多限制,但英特尔将Foveros 2.5D与EMIB 2.5D产能相结合后,其综合产能是当前行业水平的两倍以上。

目前英特尔已经完成了超过250个2.5D设计项目,这些项目既涉及英特尔产品,也涵盖其它无晶圆厂客户的需求。这些设计需要不同面积,不同数量芯片的封装,应用范围覆盖消费级产品到FPGA、服务器数据中心以及AI加速器等。因此,2.5D技术几乎涵盖了所有技术领域,并且已经非常成熟。

此外,英特尔代工还为客户提供了不少额外的增值服务。不仅是产能和各种丰富的设计经验,同时还会帮助客户优化产品,包括但不限于硅与封装的协同设计、设计策略,功率传输、高级建模,热管理,不同材料的实验室表征及相关反馈改进等方面。

在封装环节里,芯片测试也是非常重要的一项工作,确保进入封装的芯片是“已知良品”(Known Good Die,KGD)一直以来都至关重要。当一个封装内仅有一颗芯片时,情况相对简单。但如果有50块不同的芯片组合在一起,一块坏的就会毁掉另外49块好的芯片。因此确保GPU、芯片和I/O裸片都是良品变得尤为重要,以免破坏原本合格的组件。

为此,英特尔开发了多种关键技术,以确保每一个封装芯片都是已知良品。这些技术包括:

模拟裸片测试(Simulated Die Sort),确保在封装前就已经识别出良品。

EMIB的关键技术——热压结合(ThermalCompression Bonding),这使得裸片可以更高效地组装到基板上。

Foveros Direct的3D混合键合(3D Hybrid Bonding)技术。

120×120mm超大封装(Large Packages)。·应对封装尺寸变大而产生翘曲问题时,仍能够级封装(Board Assembly)的创新技术。

硅封装协同设计(SiliconPackageCo-Design)

面对AI时代的多元化需求,英特尔代工也适时调整了整体策略,以提供更加灵活的服务。例如客户可以选择英特尔的封装技术,但芯片制造可以来自其它代工厂。亦或者客户只需要英特尔的裸片测试(Die Sort)方案,英特尔也可单独提供。而在晶圆制造层面,英特尔代工也采取了相同策略,这种灵活性能够根据客户需求,为其提供更具价值的服务。

事实上,英特尔长期以来一直与台积电、三星等其它代工厂保持合作,并制定了兼容的设计规则,以确保这些代工厂生产的晶圆可以与英特尔的封装技术兼容。从而为客户提供更多选择,使其能够自由组合不同供应商的技术。

在制造领域,英特尔亚利桑那州的 Fab52 工厂 已成功完成Intel18A的流片(runthe lot),标志着该厂首批晶圆(wafer)顺利试产成功,展现了英特尔在先进制程制造方面的进展。Intel18A 节点的大规模量产(volumeproduction)将率先在俄勒冈州的晶圆厂实现,而在亚利桑那州的制造预计将于今年晚些时候进入量产爬坡阶段(rampup)。

·全新制程技术路线图公布及Intel 18A两大关键技术突破

制程技术方面,英特尔代工已与主要客户就Intel 14A制程工艺展开合作,并已经发送了Intel 14A PDK(制程工艺设计工具包)的早期版本。这些客户已经表示有意基于该节点制造测试芯片。相对于Intel 18A所采用的PowerVia背面供电技术,Intel14A将采用PowerDirect直接触点供电技术。

同时,Intel 18A制程节点已进入风险试产阶段(in risk production),并将于今年内实现正式量产(volume manufacturing)。英特尔代工的生态系统合作伙伴为Intel 18A提供了EDA支持,参考流程和知识产权许可,让客户可以基于该节点开始产品设计。

对于英特尔而言,Intel 18A制程工艺肩负着极其重要的历史使命。在这一制程节点,英特尔带来了两大技术突破——:RibbonFET全环绕栅极晶体管技术以及PowerVia背面供电技术。

RibbonFET全环绕栅极晶体管技术是破除半导体芯片因漏电而导致普遍发热问题魔咒的关键。

在芯片制程工艺不断进化的进程中,随着芯片密度不断攀升,这一问题越来越普遍和严重,RibbonFET正是应对这一挑战的有效解决方案。

通过英特尔十多年来最重要的晶体管技术创新之一,英特尔实现了全环绕栅极(GAA)架构,以垂直堆叠的带状沟道,提高晶体管的密度和能效,实现电流的精准控制,在实现晶体管进一步微缩的同时减少漏电问题发生。

与此同时,RibbonFET还能提高每瓦性能、最小电压(Vmin)操作和静电性能。无论在何种电压下,都能提供更强的驱动电流,让晶体管开关的速度更快,从而实现了晶体管性能的进一步提升。RibbonFET 还通过不同的带状宽度和多种阈值电压(Vt)类型提供了高度的可调谐性,为芯片设计带来了更高的灵活性。

晶体管作为半导体芯片最为关键的元件,会直接对性能产生影响。在日常应用中,我们格外关注PC处理器的散热问题,积热造成的处理器频率下降是影响性能体验最为直观的因素。而半导体芯片性能提升又与晶体管密度关系密切,不断缩小的芯片面积与不断增加的晶体管密度看似是一组矛盾因子,因此需要RibbonFET全环绕栅极晶体管这样的技术突破来冲破壁垒,确保更高晶体管密度下的性能释放不被电流和温度所影响。

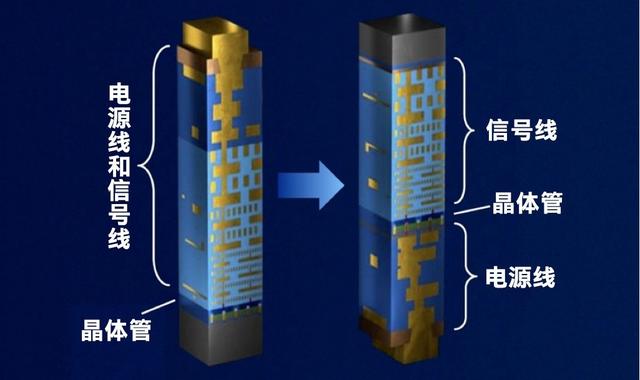

PowerVia背面供电技术也是Intel 18A制程工艺的关键技术突破。

英特尔率先在业内实现了PowerVia背面供电技术,再次革新了芯片制造。

在半导体领域,越来越多的使用场景都需要尺寸更小、密度更高、性能更强的晶体管来满足不断增长的算力需求,而混合信号线和电源一直以来都在“抢占”晶圆内的同一块空间,从而导致拥堵,并给晶体管进一步微缩增加了难度。

PowerVia背面供电技术通过将粗间距金属层和凸块移至芯片背面,并在每个标准单元中嵌入纳米级硅通孔 (nano-TSV),提高了供电效率。这项技术实现了ISO功耗效能最高提高4%,并可将标准单元利用率提升5%到10%。

在两大核心技术的支持下,Intel 18A将实现芯片性能、密度和能效的显著提升。因此与Intel 3制程工艺相比,Intel 18A的每瓦性能预计提升15%,芯片密度预计提升30%,这些改进不仅为英特尔自身产品提供了强大的性能支持,更将为诸多领域的未来创新应用奠定坚实的技术基础。

除了今年底交付的Intel 18A之外,本次英特尔代工大会最为惊喜的是公布了Intel 18A后续制程图线路,其中包括Intel 18A-P、Intel 18A-PT、Intel 14A、Intel 14A-E等。

Intel 18A制程节点的演进版本Intel 18A-P,将为更大范围的代工客户带来更卓越的性能。Intel 18A-P的早期试验晶圆(early wafers)目前已经开始生产。得益于Intel 18A-P与Intel 18A的设计规则兼容,IP和EDA合作伙伴已经开始为该演进节点提供相应的支持。

Intel 18A-PT是在Intel18A-P的性能和能效进步基础上推出的另一种Intel 18A演进版本。Intel 18A-PT可通过FoverosDirect 3D先进封装技术与顶层芯片连接,混合键合互连间距小于5微米。

英特尔代工流片的首批基于16纳米成熟制程的产品也已经进入晶圆厂生产,该制程目前主要合作伙伴是联发科。

此外,英特尔代工也正在与主要客户洽谈与UMC合作开发的12纳米节点及其演进版本。

·结语

到2035年,全球芯片代工业务规模预计可达7000亿美元,仅人工智能领域的需求,在2030年就将推动超过20% 的增长。面对产业规模升级与增长加速,同时拥有先进制程和先进封装技术的英特尔代工,未来十年必然会迎来巨大的发展机遇与挑战,而如何在成熟制造实力基础上构建更为强大的生态,如何更好地利用先进封装赋能先进制程,将是摆在英特尔代工面前的核心问题。

现在看来,无论是全球化的英特尔代工布局,丰富的封装技术组合,还是全新的英特尔制程技术路线图,以及先进制程技术突破,亦或是构建出令生态伙伴值得信赖的代工服务,都彰显着英特尔已经为迎接未来的挑战和机遇做好了准备。

(9790697)